氮化镓芯片制造全过程 技术开发的核心与未来展望

氮化镓(GaN)作为一种第三代宽禁带半导体材料,凭借其高击穿电场、高电子饱和漂移速度以及优异的耐高温和抗辐射性能,正成为功率电子、射频通信和光电子等领域技术革新的关键驱动力。其芯片制造全过程,融合了材料科学、微纳加工与器件物理的前沿技术,构成了一个精密而复杂的系统工程。

一、 技术开发的基石:材料制备与外延生长

氮化镓芯片制造始于高质量单晶材料的制备。由于缺乏同质衬底,业界普遍采用异质外延技术,主要路径包括:

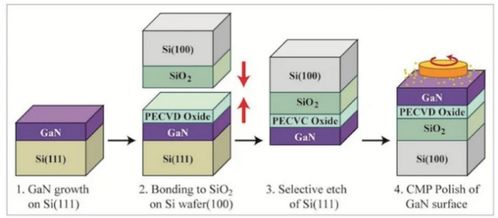

- 衬底选择:蓝宝石(Al₂O₃)、碳化硅(SiC)和硅(Si)是主流衬底。硅衬底因其大尺寸、低成本以及与现有硅基产线兼容的潜力,成为大规模商业化的重要方向,但晶格失配和热膨胀系数差异是技术挑战。

- 外延生长:金属有机化学气相沉积(MOCVD)是生产高质量氮化镓外延层的核心技术。通过精确控制反应室温度、压力、气体流量与比例,在衬底上逐层生长出氮化镓缓冲层、沟道层、势垒层等复杂异质结构,形成如高电子迁移率晶体管(HEMT)的核心功能层。

二、 核心制造工艺:微纳加工与器件成型

获得高质量外延片后,进入芯片的微观结构构建阶段,关键技术环节包括:

- 隔离工艺:通过离子注入或台面蚀刻(Mesa Isolation)形成器件之间的电学隔离区域,防止串扰。

- 欧姆接触形成:源极和漏极需要形成低电阻的欧姆接触。通常采用钛(Ti)/铝(Al)/镍(Ni)/金(Au)等多层金属堆栈,经过快速热退火(RTA)使金属与氮化镓材料合金化,降低接触电阻。

- 栅极制造:作为控制电流的开关,栅极工艺至关重要。常采用肖特基接触,使用镍(Ni)/金(Au)或铂(Pt)等金属。为提高器件频率和功率性能,T型栅、场板等复杂栅结构被广泛应用,这需要高精度的电子束光刻或步进式光刻技术。

- 表面钝化与介质沉积:氮化镓表面态会影响器件性能和可靠性。通过等离子体增强化学气相沉积(PECVD)等方法沉积氮化硅(SiNₓ)等钝化层,以稳定表面、抑制电流崩塌。层间介质(ILD)的沉积为多层互连打下基础。

- 互连与钝化:通过光刻、刻蚀和金属化(如铝或铜)工艺形成源、栅、漏的电极压焊盘(Pad)以及器件间的互连线,最后覆盖钝化层(如聚酰亚胺)进行保护。

三、 后端工艺与测试封装

制造完成的晶圆需要经过:

- 测试:进行晶圆级电学参数测试(如饱和电流、击穿电压、阈值电压等),标记不良芯片。

- 减薄与划片:将晶圆背面减薄以利于散热和封装,然后用激光或金刚石刀片将晶圆切割成单个芯片(Die)。

- 封装:根据应用需求(如射频功率放大器、快速充电器),采用不同的封装形式,如陶瓷封装、塑料封装或晶圆级封装(WLP),实现芯片与外部世界的电学连接、机械保护和高效散热。

四、 技术开发的关键挑战与未来趋势

当前氮化镓芯片技术开发聚焦于:

- 提升材料质量与降低缺陷密度:研发更优的衬底(如自支撑GaN衬底)和缓冲层技术,以提升器件性能和可靠性。

- 增强工艺集成与成本控制:推动8英寸硅基氮化镓晶圆制造技术成熟,实现与CMOS产线的深度融合,降低成本。

- 开发新器件结构与集成技术:探索垂直结构GaN器件(如CAVET)以提升功率密度,以及GaN-on-Si与硅基逻辑电路的异质集成,实现单片系统(SoC)。

- 攻克可靠性瓶颈:深入研究动态电阻退化、栅极漏电等失效机制,通过材料、工艺和电路设计的协同优化提升长期可靠性。

###

氮化镓芯片制造全过程,从外延生长到最终封装,每一个环节都凝聚着材料、工艺与设计的深度创新。随着技术开发的持续突破,氮化镓正从特定领域的“高性能选项”走向更广泛的规模化应用,有望在5G/6G通信、新能源汽车、数据中心能源管理及消费电子快充等领域,开启高效节能的半导体新时代。其制造技术的演进,不仅是单一材料的胜利,更是半导体产业向更高性能、更高效率迈进的一个缩影。

如若转载,请注明出处:http://www.shipingx.com/product/56.html

更新时间:2026-04-16 22:39:56